CMOS电路的功耗

CMOS电路

CMOS电路是目前应用最广泛的数字电路,具有面积小、功耗低且易于集成等特点,其基本原理同样适用于其他形式的数字电路。CMOS电路在理想状态下两管不同时导通,具有良好的功耗特性。CMOS集成电路功耗主要分为两个部分:静态功耗和动态功耗。

- 静态功耗

栅极氧化层的隧穿电流

反偏二极管的漏电流

电路竞争电流

MOS晶体管的亚阈导通电流等 - 动态功耗

负载电容充放电引起的开关功耗

PMOS与NMOS同时导通时产生的短路电流功耗

动态功耗占据电路总功耗的主要部分,动态功耗主要由电路中的信号翻转引起,静态功耗主要是漏电流功耗,与信号跳变频率无关。随着集成电路规模和集成度的增加,器件尺寸减小,栅极氧化层厚度减小,器件总漏电流增大,静态功耗增加。

动态功耗

动态功耗是电路运行过程中信号翻转所引起的能量消耗,主要是指电容充放电引起的功耗,即开关功耗。同时,动态功耗还包括PMOS和NMOS网络同时导通时引起的短路功耗及由于延迟引起的竞争冒险功耗等。

1.开关功耗

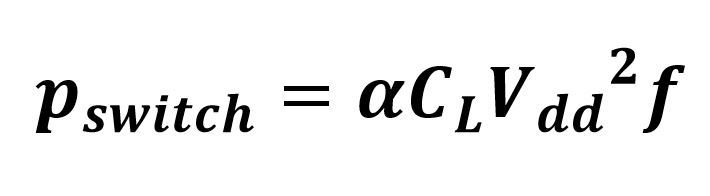

开关功耗约占CMOS电路总功耗的70%~90%,是CMOS电路低功耗设计的关键。计算公式如下:

- CL

CL包含:

自载电容(包括源漏结电容、栅极覆盖电容)

栅电容和布线之间的逻辑门扇出电容

互容产生的寄生电容

下一级电路的输入门电容

互连电容

反相器源漏区的电容 - VDD

供电电压 - f

时钟频率 - α

电路活动因子。

实际情况下,CMOS电路翻转的频率不会与时钟频率一致,即不是时钟信号每次翻转都伴随输出的翻转,α是平均时间内单个节点在单位时钟周期之内翻转的概率。

由上面的式子可以知道,开关功耗与负载电容、电源电压、工作频率及电路活动因子共同决定,减小负载电容、供电电压、工作频率和电路活动因子都可以减小动态功耗。

2.短路功耗

短路功耗约占CMOS电路总功耗的10%~30%。

对于理想的CMOS电路来说,晶体管工作状态瞬间翻转,没有延时,不存在从电源到地之间的电流通路。现实中的CMOS电路输入信号的上升/下降时间大于0,上拉网络和下拉网络在很短的时间内同时导通,存在从电源到地之间的短路电流脉冲,产生短路功耗。短路电流与CMOS管的尺寸有关。

当VDD低于PMOS和NMOS晶体管的开启电压之和时,PMOS和NMOS不满足同时导通条件,不可能同时导通,没有短路电流,但与此同时,电路的处理速率降低。

静态功耗

静态功耗主要是MOS管中的漏电流引起的功耗,占总功耗的比列不足1%。

漏电流主要与器件的工艺有关,一般由以下几个方面组成:

- 亚阈值漏电流(subthreshold leakage)

- PN结反偏电流

- 栅电流

- 栅极感应漏电流

- 沟道隧穿电流

在CMOS电路中,阈值电压非常重要。阈值电压即为形成沟道(增强型)时所对应的VGS。

电路延时与阈值电压的大小成正比,降低阈值电压可以减小电路延时。但若减小阈值电压,亚阈值电流会增大,引起漏电流功耗增加。因此在低功耗CMOS电路设计时应充分考虑阈值电压的影响,合理选择工作电压和阈值电压。漏电流功耗在总的动态功耗中所占比重较小,若选择工艺阈值电压高、栅极氧化层厚度大的晶体管,则静态功耗可以有效降低。

目前,功耗的优化方法越来越多,也越来越具有针对性,但其思想都是通过降低工作电压、工作频率、减少计算量等方法实现集成电路的功耗优化。

CMOS电路低功耗

使用CMOS电路应注意的几点:

1.CMOS电路的逻辑电平。

CMOS电路的逻辑电平与TTL电平有所区别,CMOS电路的驱动电压范围较宽,而TTL电路的驱动电压范围较窄。通常情况下,CMOS电路之间可以互相驱动,CMOS可以驱动TTL电路,而TTL并不能驱动所有的CMOS电路。

2.未用引脚的处理。

a.未用引脚不能悬空。由于CMOS电路是电压控制器件,其输入阻抗很高,如果输入引脚悬空,会带来以下问题:

- 在输入引脚上很容易积累电荷,产生较大的感应电动势。

- 输入端电平不稳定,电路来回翻转而增大系统功耗。

- 虽然CMOS器件有保护电路,不至于损坏器件,但未用引脚悬空会使输入引脚电位位于过渡区,使电路中的P沟道和N沟道都处于导通状态,致使功耗增大。

b.输出为高原则。为降低功耗,多余的门电路引脚应遵循使输出为高电平的使用原则。

3.CMOS器件的带负载能力。

CMOS电路因输入阻抗高,所以输入漏电流很小,基本可以不考虑总线带负载的能力,接口芯片可以直接挂在总线上;而TTL器件的漏电流较大,需要考虑芯片的扇出数。

4.尽量选择高速低频工作方式。

虽然CMOS器件的静态功耗几乎为零,但在逻辑电平翻转时会有电流流过,器件的动态功耗和逻辑电平翻转频率成正比。需要注意的是,选用高速低频器件会带来电磁兼容性方面的问题,因为高速器件会产生大量的谐波,产生电磁辐射。

本文标题:CMOS电路的功耗

文章作者:Mr Bluyee

发布时间:2019-01-24

最后更新:2019-07-15

原始链接:https://www.mrbluyee.com/2019/01/24/CMOS%E7%94%B5%E8%B7%AF%E7%9A%84%E5%8A%9F%E8%80%97/

版权声明:The author owns the copyright, please indicate the source reproduced.